### ՀԱՅԱՍՏԱՆԻ ՀԱՆՐԱՊԵՏՈՒԹՅԱՆ ԿՐԹՈՒԹՅԱՆ, ԳԻՏՈՒԹՅԱՆ, ՄՇԱԿՈՒՅԹԻ ԵՎ ՍՊՈՐՏԻ ՆԱԽԱՐԱՐՈՒԹՅՈՒՆ

ՀԱՅԱՍՏԱՆԻ ԱԶԳԱՅԻՆ ՊՈԼԻՏԵԽՆԻԿԱԿԱՆ ՀԱՄԱԼՍԱՐԱՆ

# Աբգարյան Գոռ Արշավիրի

ԻՆՏԵԳՐԱԼ ՄԽԵՄԱՆԵՐՈՒՄ ՓՈԽԱԶԴԵՑՈՒԹՅՈՒՆՆԵՐԻ ՀԵՏԵՎԱՆՔՆԵՐԻ ՄԵՂՄԱՑՄԱՆ ԱՐՀԵՍՏԱԿԱՆ ԲԱՆԱԿԱՆՈՒԹՑԱՄԲ ՄԻՋՈՑՆԵՐԻ ՄՇԱԿՈՒՄԸ ԵՎ ՀԵՏԱԶՈՏՈՒՄԸ

Ե.27.01 «Էլեկտրոնիկա, միկրո և նանոէլեկտրոնիկա» մասնագիտությամբ տեխնիկական գիտությունների թեկնածուի գիտական աստիձանի հայցման ատենախոսության

### ሀԵՂՄԱԳԻՐ

Երևան 2024

МИНИСТЕРСТВО ОБРАЗОВАНИЯ, НАУКИ, КУЛЬТУРЫ И СПОРТА РЕСПУБЛИКИ АРМЕНИЯ

НАПИОНАЛЬНЫЙ ПОЛИТЕХНИЧЕСКИЙ УНИВЕРСИТЕТ АРМЕНИИ

## Абгарян Гор Аршавирович

РАЗРАБОТКА И ИССЛЕДОВАНИЕ СРЕДСТВ ДЛЯ СМЯГЧЕНИЯ ПОСЛЕДСТВИЙ ПЕРЕКРЁСТНЫХ ПОМЕХ В ИНТЕГРАЛЬНЫХ СХЕМАХ С ИСПОЛЬЗОВАНИЕМ ИСКУССТВЕННОГО ИНТЕЛЛЕКТА

### **АВТОРЕФЕРАТ**

диссертации на соискание ученой степени кандидата технических наук по специальности 05.27.01- "Электроника, микро- и наноэлектроника"

Ատենախոսության թեման հաստատվել է Երևանի պետական համալսարանում (ԵՊՀ)։

Գիտական ղեկավար՝ տ.գ.դ. Վազգեն Շավարշի Մելիքյան

Պաշտոնական ընդդիմախոսներ՝ տ.գ.դ. Օլեգ Հարությունի Պետրոսյան

տ.գ.թ. Կարեն Գագիկի Մկրտչյան

Առաջատար կազմակերպություն Երևանի կապի միջոցների

գիտահետացոտական ինստիտուտ

Ատենախոսության պաշտպանությունը կայանալու է 2024թ. հուլիսի 30-ին, ժամը 10<sup>00</sup>ին, ՀԱՊՀ-ում գործող «Ռադիոտեխնիկայի և էլեկտրոնիկայի» 046 Մասնագիտական խորհրդի նիստում (հասցեն՝ 0009, Երևան, Տերլան փ., 105, 17 մասնաշենք)։

Ատենախոսությանը կարելի է ծանոթանալ ՀԱՊՀ–ի գրադարանում։

Սեղմագիրն առաքված է 2024թ. հունիսի 29-ին

046 մասնագիտական խորհրդի գիտական քարտուղար, տ.գ.թ. Բենիամին Ֆելիքսի Բադալյան

Тема диссертации утверждена в Ереванском государственном университете (ЕГУ).

Научный руководитель: д.т.н. Вазген Шаваршович Меликян

Официальные оппоненты: д.т.н. Олег Арутюнович Петросян

к.т.н. Карен Гагикович Мкртчян

Ведущая организация: Ереванский научно-исследовательский

институт средств связи

Защита диссертации состоится 30-го июля 2024 г. в  $10^{00}$  ч. на заседании Специализированного совета 046 — "Радиотехники и электроники", действующего при Национальном политехническом университете Армении (НПУА), по адресу: 0009, г. Ереван, ул. Теряна, 105, корпус 17.

С диссертацией можно ознакомиться в библиотеке НПУА.

Автореферат разослан 29-го июня 2024 г.

Ученый секретарь

Специализированного совета 046, к.т.н.

Бениамин Феликсович Бадалян

### ОБЩАЯ ХАРАКТЕРИСТИКА РАБОТЫ

Актуальность темы. Учитывая применение интегральных схем (ИС) в самых различных областях, таких как автономные автомобили, медицинское оборудование и т.д., они должны обладать высокой надежностью. В связи с этим повысились современные требования к схемам, такие как высокая скорость, целостность сигнала, низкое энергопотребление и т.д., что способствовало их развитию. Это привело к уменьшению размеров элементов до одного или нескольких n, увеличению количества транзисторов больше миллиардов, а также повышению частоты синхросигнала до нескольких TTu. В указанных условиях увеличивается количество проводников, расположенных близко друг к другу, возрастает их влияние друг на друга и уменьшается время переключения сигнала, проходящего по этим проводникам. Все это приводит к увеличению паразитных емкостей между проводниками, а также количества пар проводников, в которых присутствуют эти емкости. Следовательно, с текущим развитием ИС важным фактором, влияющим на их надежность, стали перекрёстные помехи между элементами, которые приводят к сбоям в схеме.

Для решения этой задачи как отдельные исследователи и различные научные группы, так и ведущие компании в области проектирования ИС разработали некоторые подходы, которые позволяют выявить параметры перекрёстных помех между элементами схемы и смягчить их. Однако каждый из этих подходов имеет определенные недостатки, из-за которых они не соответствуют требованиям, предъявляемым к схеме в результате ее развития, или временным требованиям к проектированию, тестированию и производству схемы. Следовательно, для решения этой проблемы требуются новые подходы.

Диссертационная работа посвящена разработке методов и принципов обнаружения последствий перекрёстных помех между элементами в ИС, которые позволят предложить варианты смягчения этих последствий путем изменения дерева синхросигнала (ДС) и проводников, несущих информацию.

<u>Объект исследования.</u> Объектом исследования являлись перекрёстные помехи между элементами в ИС, методы их смягчения, а также алгоритмы и модели искусственного интеллекта (ИИ).

<u>Цель работы.</u> Прогнозирование перекрёстных помех между элементами на основе информации о проводниках интегральных схем и проходящих через них сигналах, а также их смягчение с учетом особенностей проектирования схемы.

<u>Методы исследования.</u> Исследованы современные подходы к моделированию перекрёстных помех между элементами в ИС и оценке их последствий, методы получения моделей ИИ на основе базы данных и формы их применения.

### Научная новизна:

- Предложены подходы к обнаружению, анализа и смягчению перекрёстных помех между элементами, которые при незначительном ухудшении их характерных параметров обеспечивают экономию времени обнаружения, а при незначительном увеличении площади и энергопотребления смягчение последствий перекрёстных помех и общих временных параметров.

- Разработан метод прогнозирования перекрёстных помех между элементами в ИС на основе алгоритмов машинного обучения, который за счет минимального

сбора данных и анализа схемы обеспечивает экономию времени на анализ целостности сигнала примерно на 36,6% при потере прогнозируемых данных ~10%.

- Предложен метод к изменению соответствующих проводников с учетом архитектуры дерева синхросигнала и особенностей проектирования схемы, который благодаря оптимизированной комбинации экранирования и блокировок при перемещении проводников дерева синхросигнала обеспечивает смягчение последствий перекрёстных помех примерно на 17,9%, сокращение общего времени размещения и хранения последовательных элементов - на 16,9% и 19,1% соответственно при потере энергии примерно на 5,66% и площади - на 3,1%.

- Созлан метол оценки информационных проводов соответствующих проводов с учетом особенностей проектирования схем, который благодаря оптимизированному сочетанию экранирования обеспечивает размещения повторителей уменьшение возлействия перекрёстных помех примерно на 17%, уменьшение общих времен установки и удержания последующего элемента - на 16,3% и 17,6% соответственно при потере потребления энергии около 3% и плошади - на 2.9%.

Практическая ценность работы. Разработано программное средство (ПС) "Crosstalk Detection and Compensation Tool" (CDACT), выполняющее прогнозирование перекрёстных помех между элементами и предлагающее решения лля их смягчения. При использовании ПС в случае изменения проводников ЛС достигается смягчение перекрёстных помех на 15.3%, сокрашение общего времени размещения и хранения последовательных элементов - на 14,1% и 15,9% соответственно при потере площади на 2,91% и энергии - на 4,58%. В случае информацию. достигается смягчение проводников. несущих перекрёстных помех на 15%, сокращение общего времени размещения и хранения последовательных элементов на 13,6% и 14,6% соответственно при потере площади на 2,7% и энергии - на 2,7%.

### На защиту выносятся следующие научные положения:

- Метод прогнозирования перекрёстных помех между элементами в интегральных схемах на основе алгоритмов машинного обучения (МО):

- метод изменения соответствующих проводников с учетом архитектуры ДС и особенностей проектирования схемы;

- метод изменения соответствующих проводников с учетом оценки проводников, несущих информацию, и особенностей проектирования схемы;

- программное средство, выполняющее прогнозирование перекрёстных помех между элементами и предлагающее решения для их смягчения.

<u>Достоверность</u> научных положений подтверждается представленными в диссертации экспериментальными результатами схемотехнического моделирования и математическими обоснованиями.

**Внедрение.** Разработанное ПС CDACT был внедрен в ООО "Сиско Интернетворкинг" и используется на различных этапах проектирования схем для прогнозирования перекрёстных помех между элементами и получения рекомендаций по смягчению их последствий.

<u>Апробация работы.</u> Основные научные и практические результаты диссертации докладывались на:

- Международном симпозиуме "IEEE East-West Design & Test" (Батуми, Грузия, 2023);

- научных семинарах кафедры "Микроэлектронные схемы и системы" НПУА (Ереван, Армения, 2021 - 2024 гг.);

- научных семинарах ЗАО "Синопсис Армения" (Ереван, Армения, 2021 -2024 гг.).

<u>Публикации.</u> Основные положения диссертации представлены в восьми научных работах, список которых приведен в конце автореферата.

Структура и объем диссертации. Диссертация состоит из введения, трех глав, основных выводов, списка литературы, включающего 132 наименования, и четырех приложений. В первом приложении представлен акт внедрения, во втором - отрывок описания схемы GDT, использованной для прогнозирования перекрёстных помех между элементами, в третьем - отрывок описания разработанного программного инструмента CDACT, в четвертом - списки рисунков, таблиц и сокращений. Основной объем диссертации составляет 119 страниц, а вместе с приложениями - 161 страницу. Диссертация написана на армянском языке.

### ОСНОВНОЕ СОДЕРЖАНИЕ РАБОТЫ

<u>Во введении</u> обоснована актуальность темы диссертации, сформулированы цель и основные задачи исследования, представлены методы исследования, научная новизна, практическое значение и основные научные положения, выносимые на защиту.

<u>В первой главе</u> рассматриваются причины возникновения перекрёстных помех между элементами в интегральных схемах, их последствия и характерные параметры.

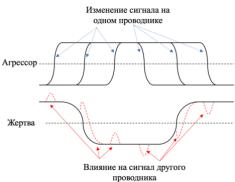

Перекрёстные помехи в ИС возникают между проводниками агрессор-жертва (рис. 1).

Puc. 1. Влияние изменения сигнала одного проводника на сигнал другого проводника

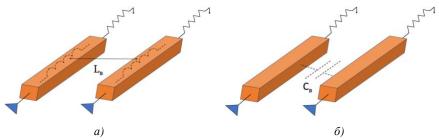

Перекрёстные помехи могут возникать из-за взаимной индуктивности (рис. 2 а) или из-за взаимной емкости (рис. 2 б).

Рис. 2. Взаимная индуктивность (а) и емкость (б) между проводниками

В первом и во втором случаях соответствующие изменения напряжения и тока на жертве со стороны агрессора описываются следующим образом:

$$V_{\text{H}} = L_{\text{B}} * \frac{dI_{\text{a}}}{dt}, \tag{1}$$

$$I_{\text{H}} = C_{\text{B}} * \frac{dV_{\text{a}}}{dt}, \tag{2}$$

$$I_{\rm H} = C_{\rm B} * \frac{dV_{\rm a}}{dt},\tag{2}$$

где L<sub>в</sub> - взаимная индуктивность между агрессором и жертвой; I<sub>а</sub> - ток на агрессоре;  $C_B$  - взаимная емкость между агрессором и жертвой;  $V_a$  - напряжение на агрессоре.

В ИС перекрёстные помехи между элементами стали важным вызовом по нескольким причинам:

- увеличение количества элементов в ИС приводит к уменьшению расстояния между ними. Уменьшение расстояния между проводниками увеличивает взаимную емкость между ними, следовательно, уменьшает емкостное сопротивление. Это означает, что изменение уровня напряжения на агрессоре приведет к увеличению тока на жертве;

- увеличение скорости ИС уменьшает емкостное сопротивление между элементами. Снова, изменение уровня напряжения на агрессоре приведет к увеличению тока на жертве;

- изменение уровня напряжения на агрессоре уже может привести к изменению логического уровня напряжения на жертве, так как рабочие напряжения схемы уменьшились;

- кроме вышеупомянутого, перекрёстные помехи могут вызвать изменение временных параметров сигнала на жертве проводника.

До сегодняшнего дня различными научными группами или отдельными специалистами разрабатывались методы и подходы для рассмотрения, решения и проверки перекрёстных помех, которые имеют множество преимуществ друг перед другом, однако все они не лишены недостатков. Предлагаемые методы предполагают внесение изменений как в физический, так и в логический проект схемы. Однако с текущим развитием ИС такие решения уже могут быть недостаточными для обнаружения, рассмотрения и устранения возникающих сбоев.

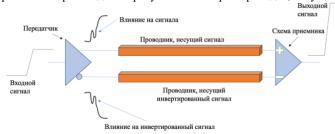

использования дифференциального сигнала. предполагает наличие в схеме сразу двух проводников, несущих сигнал: на одном будет исходный сигнал, на другом - его инвертированная версия (рис. 3). Однако для достижения такого результата от разработчиков и производителей при проектировании и производстве требуется симметрия проводов, несущих сигнал.

Рис. 3. Выходной сигнал с использованием дифференциального сигнала

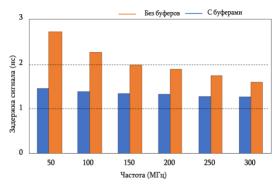

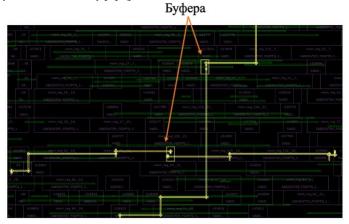

**Метод использования буферов.** В схеме при обычной подстановке проводников влияние агрессора на жертву зависит от взаимной емкости между ними. Жертва, располагающаяся вдоль агрессора, заменяется на отдельные компоненты с использованием буферов (рис. 4).

Рис. 4. Расположение проводников в схеме с использованием буферов

Этот метод оптимизирует задержку сигналов, проходящих по данному проводу (рис. 5).

Рис. 5. Задержка сигнала в зависимости от частоты с использованием буферов

Таким образом, уменьшается площадь перекрытия между проводниками, соответственно уменьшается взаимная емкость, снижая влияние на каждый участок проводника.

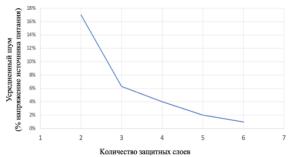

**Метод экранирования.** Предлагается внедрение защитных проводников между информационными проводниками, что более известно под термином "экранирование". Применение экранирования уменьшает влияние агрессора на жертву, и, в зависимости от количества защитных слоев, это влияние становится еще меньше (рис. 6).

Рис. 6. Влияние агрессора на жертву в зависимости от количества зашитных слоев

Влияние агрессора на жертву уменьшается не только за счет увеличения количества защитных слоев, но и за счет изменения их размеров (рис. 7).

Рис. 7. Влияние агрессора на жертву в зависимости от ширины зашитных слоев

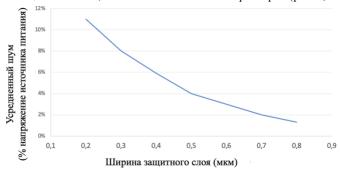

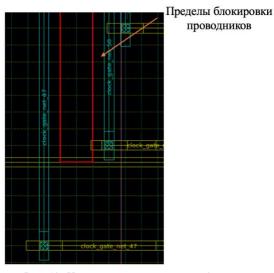

**Блокировка маршрутизации.** Предлагается в процессе проектирования схемы, когда соответствующее ПС создает данный проводник в схеме, установить определенные зоны блокировки, в которых нельзя выполнять проектирование проводников (рис. 8). Такие границы представляют собой прямоугольные зоны, для которых задаются координаты и соответствующий металлический уровень.

Схема, на которой проводились испытания, имеет 100 доступных путей для проектирования металлов на одном уровне металлизации, однако в данной схеме

этими путями проходит 172. Применяя метод блокировки маршрутизации используя 70% ресурсов проектирования металлов, в данном участке схемы были исключены металлические соединения.

Рис. 8. Изменение схемы с помощью блокировки

<u>Во второй главе</u> представлены разработанные методы и даны решения проблем, описанных в первой главе.

Метод прогнозирования перекрёстных помех в ИС. Для применения предлагаемого метода обнаружения перекрёстных помех в ИС предоставляются файлы с расширениями GDSII и nlib, полученные в результате физического проектирования схемы, а также текстовый файл соответствия кодирования элементов ИС для данного технологического процесса. Для экономии ресурсов, используемых для реализации принципа, также применяется определенная дополнительная информация. Для реализации предложенного принципа производится сбор данных из вышеуказанных файлов и вспомогательной информации, затем на основе этих данных создается модель МО для прогнозирования перекрёстных помех в ИС.

Сначала осуществляется декодирование входных данных и сбор необходимых данных. Выводятся:

- координаты первого и второго металлов;

- расстояние между ними, площадь перекрытия, коэффициент взаимной емкости, уровень металла;

- минимально допустимое расстояние между проводниками для уровня металла;

- при наличии индикатора наклонных металлов в схеме индикаторы наклонных металлов для первого и второго металлов;

- индикаторы принадлежности первого и второго металлов к ДС или к информационным проводникам, а также частота синхросигнала в случае части ДС и активность изменения сигнала в случае информационного проводника.

Затем выполняется анализ целостности сигнала схемы, и извлекается коэффициент влияния для выбранной пары металлов. Этот коэффициент показывает задержку другого сигнала, вызванную изменением одного сигнала. Выполняются действия, предусмотренные для модели: подготовка информации, нормализация данных, выбор функций активации нейронов, построение и обучение МО.

Использование метода прогнозирования взадиодествий в ИС представлено на рис. 9.

Рис. 9. Обзор предлагаемого принципа

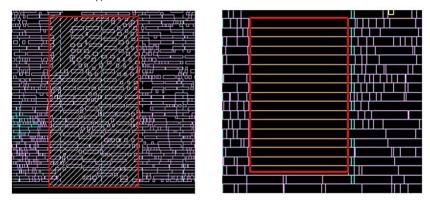

Для обучения модели МО использовалась схема, спроектированная с ячейками учебной библиотеки SAED14. В схеме содержится 22826 стандартных ячеек, площадь составляет 9140,6141 мкм², общая длина проводов, составляющих ДС, составляет 7781,291 мкм, утилизация логических ячеек - 60,34%. Время, затраченное на автоматическую расстановку и обвязку схемы с использованием программного обеспечения, составило 8227,7 с. Схема была спроектирована с входным синхросигналом в 2 ГГи. В качестве функции потерь выбрана среднеквадратичная ошибка. Она достигает своего минимального значения в течение 50 циклов (рис. 10).

Рис. 10. Функция потерь модели в зависимости от количества циклов

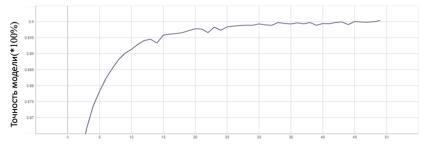

В ходе исследования было установлено, что при обучении в течение 48...53 циклов точность модели прогнозирования перекрёстных помех составляет около 91% (рис. 11).

Рис. 11. Точность модели в зависимости от количества циклов

Принцип оценки и предложения изменений проводников дерева синхросигнала (ДС) в ИС. Предлагается на основе модели вместо полной модификации архитектуры ДС выполнять изменения в отдельных её участках, используя оптимизированные комбинации уже существующих методов снижения перекрёстных помех. Для выбранного диапазона значений площади перекрытия между элементами оценивается расстояние между ними, и по результатам этой оценки вносятся соответствующие изменения в провода ДС.

Если расстояние между проводами меньше тройного минимально допустимого расстояния между проводами для данного уровня металла, то для таких проводов применяется установка блокировок, и проект выполняется с учетом этого ограничения (рис. 12).

Рис. 12. Изменение смещения проводов после применения блокировки

В противном случае, когда расстояние между проводами превышает тройное минимально допустимое расстояние между проводами для данного уровня металла, для этих проводов применяется метод экранирования (рис. 13).

### Экранирующий проводник

Рис. 13. Перекомпоновка проводов после экранирования

Для реализации принципа из результатов прогнозирования перекрёстных помех выделяются все пары металлических проводников, из которых хотя бы один проводник принадлежит ДС. По отдельности реализованы методы, известные из литературы, которые затем были объединены с результатами, полученными в результате применения модели МО (табл. 1).

Таблица 1 Сравнение временных параметров до и после реализации предложенного принципа изменения проводников ДС

| Параметер               |            |            | Временное      |  |  |

|-------------------------|------------|------------|----------------|--|--|

|                         | Суммарное  | Суммарное  | отклонение,    |  |  |

| Форма<br>проектирования | время      | время      | обусловленное  |  |  |

|                         | нарушения  | нарушения  | перекрёстными  |  |  |

|                         | установки, | удержания, | помехами между |  |  |

|                         | nc         | nc         | элементами,    |  |  |

|                         |            |            | nc             |  |  |

| Начальная схема         | -1121,6    | -411,6     | -10,9075       |  |  |

| С экранированием        | -1024,0208 | -368,382   | -10,0894       |  |  |

| С блокировками          | -1049,8176 | -384,0228  | -9,9258        |  |  |

| Предлагаемый принцип    | -931,7131  | -332,9432  | -8,9529        |  |  |

<u>Принцип</u> оценки и изменения информационных проводников в интегральных схемах. Предлагается на основе полученной модели, после внесения изменений в отдельные участки ДС, провести дополнительные модификации для линий передачи данных, используя уже существующие оптимизированные комбинации методов уменьшения влияния перекрёстных помех, и далее для выбранного диапазона значений площади взаимного перекрытия между элементами оценить расстояние между ними и на основе этой оценки внести соответствующие изменения в информационные провода.

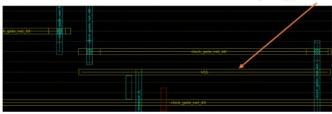

Если расстояние между проводами меньше, чем утроенное минимально допустимое расстояние между проводами для данного уровня металла, то на эти провода устанавливается буфер (рис. 14).

Рис. 14. Изменение взаимного расположения проводов после установки повторителей

В противном случае, когда между проводами возможно разместить дополнительные провода, выполняется экранирование проводов (рис. 15).

# Экранирующий проводник

Puc. 15. Взаимное расположение проводов после экранирования

Увеличение числа повторителей в схеме предполагает добавление дополнительных транзисторов. В этом случае после добавления транзисторов любой провод должен быть подключен до металла уровня один. Следовательно, для повышения эффективности применения предложенного метода в металлическом уровне один выполнена только установка буферов. Затем для остальных уровней

выполнены вышеуказанные модификации. Для применения предложенного принципа из полученных предсказаний перекрёстных помех выделяются все пары металлических проводов, ни один из которых не принадлежит ДС. Было выполнено экранирование между металлами схемы, затем произведена установка буферов. После этого была произведена оптимизированная комбинация двух методов (табл. 2).

Таблица 2 Сравнение временных параметров до и после реализации предложенного принципа изменения проводников передачи данных

| Параметер            |            |            | Временное      |  |

|----------------------|------------|------------|----------------|--|

|                      | Суммарное  | Суммарное  | отклонение,    |  |

|                      | время      | время      | обусловленное  |  |

| Форма проектирования | нарушения  | нарушения  | перекрёстными  |  |

|                      | установки, | удержания, | помехами между |  |

|                      | nc         | nc         | элементами,    |  |

|                      |            |            | nc             |  |

| Начальная схема      | -1121,6    | -411,6     | -10,9075       |  |

| С экранированием     | -1036,3584 | -373,3212  | -10,024        |  |

| С буфером            | -1022,8992 | -367,1472  | -9,8386        |  |

| Предлагаемый принцип | -938,779   | -339,16    | -9,053         |  |

<u>В третьей главе</u> представлен разработанный полностью автоматизированный программный инструмент CDACT, который, при необходимости, может применяться как для разработки, обучения и сохранения моделей, так и для использования вышеупомянутых моделей и извлечения данных о последствиях перекрёстных помех в ИС при наличии соответствующих данных. Основанный на модели полностью автоматизированной системы, программный инструмент позволяет прежде всего систематизировать выполняемые рабочие цепочки и исключить ошибки, связанные с человеческим фактором.

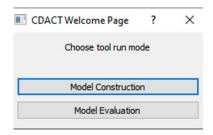

Сначала запуск программного средства позволяет выбрать его рабочий режим (рис. 16): режим обнаружения перекрёстных помех с помощью автоматизированного потока, автоматического построения и обучения моделей, или предоставления

Рис. 16. Окно выбора рабочего режима

возможности делать определенные наблюдения на основе данных, полученных в результате применения уже построенных моделей.

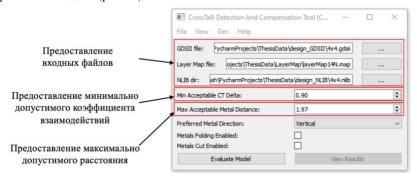

Рабочий режим "Model Construction" представляет собой автоматизированный поток для получения модели МО, а также режим просмотра результатов обучения данных, использованных для обучения уже построенной модели МО (рис. 17).

| CrossTalk Detection And Compensation Tool (CDACT) |              |  |  | × |

|---------------------------------------------------|--------------|--|--|---|

| File View Gen Help                                |              |  |  |   |

| GDSII file:                                       |              |  |  |   |

| Layer Map file:                                   |              |  |  |   |

| NLIB dir:                                         |              |  |  |   |

| Preferred Metal Direction:                        | Horizontal   |  |  | ~ |

| Metals Folding Enabled:                           |              |  |  |   |

| Metals Cut Enabled:                               |              |  |  |   |

| Build Model                                       | View Results |  |  |   |

Рис. 17. Окно рабочего режима построения модели

В отличие от режима построения модели, в рабочем режиме "Model Evaluation" разрешается указывать определенные значения, используемые для извлечения данных, на основе которых будут сделаны последующие выводы по результатам применения модели (рис. 18).

Рис. 18. Окно предоставления входной информации для применения модели

После ввода вышеуказанных данных, а также проверки и применения модели МО на основе полученных данных активируется кнопка "View Results", которая позволяет в отдельном окне увидеть коэффициенты перекрёстных помех, предсказанные моделью МО для существующих данных.

Кнопка "View Results" в режиме построения модели изначально находится в пассивном состоянии и активируется только после завершения построения,

обучения и тестирования модели МО. Относительная ошибка определяется математически, на основе реальных и предсказанных данных:

$$rel_{\text{ошибка}} \frac{abs(x_i - x_i')}{x_i} * 100\%,$$

(3)

где  $rel_{\text{ошибка}}$  - относительная ошибка реальных и предсказанных значений;  $x_i$  и  $x_i'$  - соответственно предсказанное и реальное значения данных.

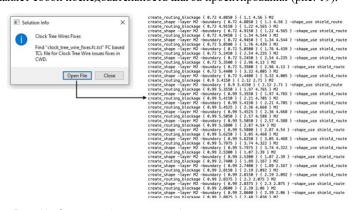

Меню "Gen" разделено на две части для соответствующих методов снижения перекрёстных помех. Выбрав подменю "Clock tree fixes" в меню "Gen", программное средство сразу создает файл с соответствующим расширением, который представляет собой последовательность шагов проектирования (рис. 19).

Рис. 19. Окно отображения предложений по смягчению влияния перекрёстных помех для проводов ДС

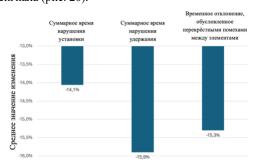

Из анализа результатов видно, что средние изменения временных параметров в различных схемах с использованием ПС имеют следующий вид после изменений в проводах синхросигнала (рис. 20).

Рис. 20. Средние значения изменений временных параметров, полученные после изменений проводов синхросигнала в различных схемах

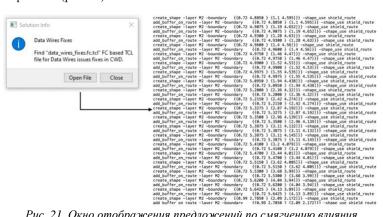

Выбрав подменю "Data wire fixes" в меню "Gen", CDACT немедленно создает файл с соответствующим расширением для программного инструмента для проектирования схем, в котором содержится последовательность шагов проектирования (рис. 21).

Puc. 21. Окно отображения предложений по смягчению влияния перекрёстных помех на информационные провода

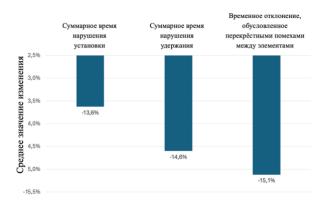

Из анализа результатов следует, что при применении ПС усредненные результаты изменений временных параметров в различных схемах имеют следующий вид после изменений информационных проводов (рис. 22).

Рис. 22. Средние значения изменений временных параметров, полученные после изменений информационных проводов в различных схемах

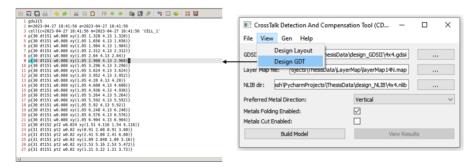

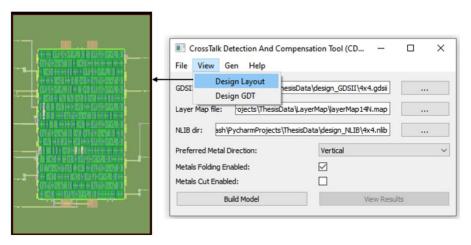

Подменю "View" в главном меню предназначено для просмотра как входного файла с расширением GDSII, так и выходного файла с расширением GDT. В

частности, GDT - это файл с текстовым расширением, который можно просмотреть с помощью любого текстового редактора (рис. 23).

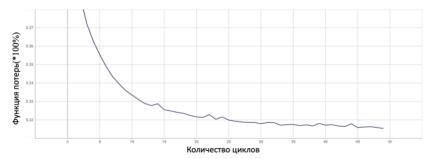

Рис. 23. Окна отображения файла GDT

А для просмотра файла с расширением GDSII используется кнопка "Design Layout" (рис. 24).

Рис. 24. Окно просмотра файла схемы с расширением GDSII

### ОСНОВНЫЕ ВЫВОДЫ ПО ДИССЕРТАЦИОННОЙ РАБОТЕ

- 1. Предложены подходы к обнаружению, анализа и смягчению перекрёстных помех между элементами, которые при незначительном ухудшении их характерных параметров обеспечивают экономию времени обнаружения, а при незначительном увеличении площади и энергопотребления смягчение последствий перекрёстных помех и общих временных параметров [1-8].

- 2. Разработан метод прогнозирования перекрёстных помех между элементами в ИС на основе алгоритмов машинного обучения, который за счет минимального сбора данных и анализа схемы обеспечивает экономию времени на анализ целостности сигнала примерно на 36,6% при потере прогнозируемых данных ~10% [1, 2, 8].

- 3. Предложен метод к изменению соответствующих проводников с учетом архитектуры дерева синхросигнала и особенностей проектирования схемы, который благодаря оптимизированной комбинации экранирования и блокировок при перемещении проводников дерева синхросигнала обеспечивает смягчение последствий перекрёстных помех примерно на 17,9%, сокращение общего времени размещения и хранения последовательных элементов на 16,9% и 19,1% соответственно при потере энергии примерно на 5,66% и площади на 3,1%. [1, 2, 5-7].

- 4. Создан метод оценки информационных проводов и изменения соответствующих проводов с учетом особенностей проектирования схем, который благодаря оптимизированному сочетанию экранирования и размещения повторителей обеспечивает уменьшение воздействия перекрёстных помех примерно на 17%, уменьшение общих времен установки и удержания последующего элемента на 16,3% и 17,6% соответственно при потере потребления энергии около 3% и площади на 2,9% [1, 2, 5-7].

- 5. Разработано программное средство «Crosstalk Detection and Compensation Tool» (CDACT), выполняющее прогнозирование перекрёстных помех между элементами и предлагающее решения для их смягчения, при использовании которого случае изменения проводников синхросигнального дерева достигается смягчение перекрёстных помех на сокращение общего времени установки последовательных элементов на 14,1% и 15,9% соответственно, при этом происходит потеря площади на 2,91% и энергии на 4,58%, в случае изменения проводников, несущих информацию, достигается смягчение перекрёстных помех на 15%, сокращение общего времени установки и удержания последовательных элементов на 13,6% и 14,6% соответственно, при этом происходит потеря площади на 2,7% и энергии на 2,7%.

Основные результаты диссертации опубликованы в следующих работах:

1. Abgaryan G.A. A Built-in Self-Test System for External DRAM // Mathematical Problems of Computer Science. -2020. - Vol. 54. − P. 80−87, doi: https://doi.org/10.51408/1963-0061

- 2. Աբգարյան Գ.Ա., Բաբայան Ա.Վ. Generic bist architecture for memories // ՀՀ ԳԱԱ և ՀԱՊՀ-ի Տեղեկագիր. Տեխն. Գիտ. Սերիա. 2021. Հատ. 74, no. 2 P. 204-209

- 3. Մխիթարյան Ա.Խ., Աբգարյան Գ.Ա., Պետրոսյան Պ.Ս., Ավագյան Ն.Ա.14 նմ տեխնոլոգիական գործընթացի համար ծերացման հատկությունների հետազոտումը արագագործ համեմատիչի օրինակով // Վանաձորի պետական համայսարանի գիտական տեղեկագիր. Երևան, 2021. էջ. 21-29.

- Melikyan V., Abgaryan G., Petrosyan P., Avakyan N. Low Power Analogue-Digital Converter Model // Journal of Contemporary Physics (Armenian Academy of Sciences). - July, 2021. - Vol. 56, no. 3. - P. 275-279, doi: https://doi.org/10.3103/s1068337221030178

- Abgaryan G.A., Galstyan A.A., Harutyunyan G.A. Reduction consequences of the wire interconnections in integrated circuits by optimizing of the clock tree // Proceedings of the NAS RA and NPUA. - Series of Technical Sciences. - 2022. - Vol. 75, no 4, - P. 424-430

- Melikyan V., Petrosyan P., Avagyan N., Abgaryan G. Self-heating analysis method of integrated circuits // International Conference on Microwave & THz Technologies, Wireless Communications and OptoElectronics (IRPhE 2022). - Yerevan, Armenia, 2022. - Vol. 41. - P. 63-65, doi: 10.1049/icp.2022.2799

- Melikyan V., Petrosyan P., Avagyan N., Abgaryan G. Smart Adjustment Of Transistor Parameters To Reduce Temperature Rise Due To Self-Heating Effect // 2023 IEEE East-West Design & Test Symposium (EWDTS). - Batumi, Georgia, 2023. - P. 1-5, doi: 10.1109/EWDTS59469.2023.10297080.

- 8. Abgaryan G. Crosstalk Prediction In Integrated Circuits Based on Machine Learning Techniques // 2023 IEEE East-West Design & Test Symposium (EWDTS). Batumi, Georgia, 2023. P. 1-5, doi: 10.1109/EWDTS59469.2023.10297079.

### ገብብ፤መበውፒ፤፤፤

Ներկայումս ինտեգրալ սխեմաները օգտագործվում են ամենատարբեր ոլորտներում, ներառյալ ինքնավար ավտոմեքենաներում, սարքավորումներում և այլն։ Հետևաբար, սխեմաներից պահանջվում է ունենանալ բարձր հուսալիություն։ Իսկ նշված ոլորտներում կիրառությունը ինտեգրալ սխեմաների վրա դրել է բարձր արագագործության, ազդանշանի ամբողջականության, գածր էներգասպառման և այլ պահանջներ, ինչը նպաստել է դրա ցարգացմանը։ Վերջինս բերել է նրան, որ սխեմայում տարրերի չափսերը հասել են մեկ կամ մի քանի *նմ*-ի, տրանցստորների քանակը անցել է միլիարդից, սինքրոացդանշանը հասել է 92q-եր հաճախության։ Այս ամենի հետևանքով հաղորդալարերով փոթոանում է սխեմայի անցնող ազդանշանի փոխանջատման ժամանակը, ավելանում են իրար մոտ գտնվող դողերի քանակը, ինչպես նաև մեծանում է դրանց ազդեցությունը իրար վրա։ Ուրեմն, լարերի միջև գոլություն ունեցող մակաբուծային ունակությունները մեծանում են, ինչպես նաև շատանում են այն հաղորդայարերի ցույգերի քանակը, որոնցում առկա են այդ ունակությունները։ Այս ամենից պարզ է դառնում, որ ինտեգրալ սխեմաների հուսալիության վրա ազդող գործոններից կարևոր է դարձել դրանցում տարրերի միջև փոխազդեցությունները։

Մխեմայի հուսալիության վրա ազդող այս կարևոր հիմնահարցի լուծման համար տարբեր գիտական խմբեր և ինտեզրալ սխեմաների նախագծման ոլորտի առաջատար ընկերություններ առաջարկել են տարբեր մեթոդներ, որոնցով հնարավորություն է ստեղծվում դուրս բերել սխեմայի տարրերի միջև փոխազդեցություններին բնորոշ պարամետրերը և մեղմացնել դրանք։ Լուծումներից լուրաքանչյուրում առաջարկվում է սխեմալում կատարել որոշակի փոփոխություններ ինչպես տրամաբանական, այնպես էլ ֆիզիկական նախագծման փուլերում։ Սակայն մոտեցումներից լուրաքանչյուրն ունի որոշակի թերություն՝ այն փոխազդեցություններին բնորոշող պարամետրերի լավացման հետ միաժամանակ վատացնում է սխեմայի այլ կարևոր պարամետրեր, ինչպիսիք են մակերեսը, էներգասպառումը, ինչպես նաև ավելացնում են սխեմայի նախագծման ժամանակը և բարդությունը, որի պատձառով չեն բավարարում սխեմալի զարգացման հետևանքով դրա վրա որված պահանջներին, սխեմայի նախագծման, թեստավորման և արտադրման ժամանակային պահանջներին։ Ուստի, այս հիմնահարգի յուծման համար պահանջվում են նոր մոտեցումներ։

Ատենախոսությունը նվիրված է ինտեգրալ սխեմաներում տարրերի միջև փոխազդեցությունների հետևանքների հայտնաբերման մեթոդների և սկզբունքների մշակմանը, որոնք թույլ կտան առաջարկել այդ հետևանքների մեղմացման տարբերակներ՝ համապատասխանաբար սինքրոազդանշանային ծառի և տեղեկատվություն կրող լարերի փոփոխություններ կատարելով։

Առաջարկվել են տարրերի միջև փոխազդեցությունների հատնաբերման, վերլուծության և մեղմացման եղանակներ, որոնք դրանց բնորոշ պարամետրերի ոչ էական վատթարացմամբ ապահովում են հայտնաբերման ժամանակի խնայողություն, մակերեսի և էներգասպառման ոչ էական մեծացմամբ ապահովում են փոխազդեցությունների հետևանքների և ընդհանուր ժամանակային պարամետրերի մեղմացում։

Մշակվել է ինտեգրալ սխեմաներում տարրերի միջև փոխազդեցությունների կանխատեսման համար մեքենայական ուսուցման ալգորիթմերի վրա հիմնված եղանակ, որը, հնարավորինս քիչ տվյալների հավաքագրման և սխեմայի վերլուծության հաշվին, ապահովում է ազդանշանի ամբողջականության վերլուծության վրա ծախսվող ժամանակի մոտավորապես 36,6% խնայողություն, կանխատեսված տվյալների մոտ 10% կորստի հաշվին։

Առաջարկվել է սինքրոացրանշանային ծառի ձարտարապետության նախագծման գնահատման սխեմայի առանձնահատկությունների դիտարկմամբ համապատասխան հաղորդալարերի փոփոխության մեթոդ, որը, ենոանավոոման արգելափակումների լավարկված համադրությամբ lı սինթրոագդանշանային ծառի լարերի տեղափոխության շնորհիվ, ապահովում է փոխազդեցություններիի հետևանքների մոտավորապես 17,9%, հաջորդական տարրի մուտքի տեղակալման և պահպանման ընդհանուր ժամանակների համապատասխանաբար 16,9% և 19,1%-ով մեղմացում, էներգասպառման մոտ 5,66% և մակերեսի 3,1% կորստի հաշվին։

Մտեղծվել է տեղեկատվություն կրող լարերի գնահատման և սխեմայի նախագծման առանձնահատկությունների դիտարկմամբ համապատասխան հաղորդալարերի փոփոխության եղանակ, որը, էկրանավորման և կրկնիչների լավարկված համադրությամբ հաղորդալարերի ծրագծման շնորհիվ, ապահովում է փոխազդեցությունների հետևանքների մոտավորապես 17%, հաջորդական տարրի մուտքի տեղակայման և պահպանման ընդհանուր ժամանակների համապատասխանաբար 16,3% և 17,6%-ով մեղմացում, էներգասպառման մոտ 3% և մակերեսի 2,9% կորստի հաշվին։

Մշակվել է տարրերի միջև փոխագրեցությունների կանխատեսում իրականացնող և մեղմացման լուծումներ առաջարկող «Crosstalk Detection and Compensation Tool» (CDACT) ծրագրային uhongn, nnh սինքրոագդանշանային ծառի լարերի փոփոխության դեպքում ստացվում է փոխազդեցությունների 15,3%, հաջորդական տարրերի մուտքի տեղակալման և պահպանման ընդհանուր ժամանակների համապատասխանաբար 14,1% և 15,9% մեղմացում, մակերեսի 2,91% և էներգասպառման 4,58% կորստի հաշվին, դեպքում՝ տեղեկատվություն փոփոխության կրող լարերի փոխազդեցությունների 15%, հաջորդական տարրերի մուտքի տեղակայման և պահպանման ընդհանուր ժամանակների համապատասխանաբար 13,6% և 14,6% մեղմացում, մակերեսի 2,7% և էներգասպառման 2,7% կորստի հաշվին։

### GOR ARSHAVIR ABGARYAN

# DEVELOPMENT AND STUDY OF TOOLS FOR MITIGATING THE CROSSTALK IN INTEGRATED CIRCUITS USING ARTIFICIAL INTELLIGENCE

### SUMMARY

Nowadays, integrated circuits are used in various fields, including autonomous vehicles, medical equipment, and more. Therefore, these circuits are required to have high reliability. The application of integrated circuits in these fields has placed demands on high performance, signal integrity, low power consumption, and other requirements, which have driven its development. This has led to the size of elements in the circuit reaching one or several nanometers, the number of transistors exceeding billions, and the clock signal reaching frequencies of GHz. As a result, the switching time of signals passing through the circuit wires decreases, the number of wires located close to each other increases, and their influence on each other grows. Consequently, the parasitic capacitance existing between the wires increases, as well as the number of wire pairs in which these capacitances are present. All this makes it clear that one of the important factors affecting the reliability of integrated circuits is the interactions between elements within them.

To address this critical issue affecting circuit reliability, various scientific groups and leading companies in the field of integrated circuit design have proposed different methods that enable the extraction and mitigation of parameters characteristic of interactions between circuit elements. Each solution proposes making certain changes to the circuit at both logical and physical design stages. However, each approach has certain drawbacks; while improving the parameters characteristic of these interactions, they simultaneously degrade other important parameters of the circuit, such as area, power consumption, and also increase the design time and complexity. As a result, they fail to meet the requirements imposed on the circuit due to its development, as well as the time demands for design, testing, and production of the circuit. Therefore, new approaches are needed to solve this issue.

The dissertation is dedicated to the development of methods and principles for detecting the consequences of interactions between elements in integrated circuits, which will allow for proposing options for mitigating these consequences by making changes to the synchronization signal tree and information-carrying wires accordingly.

Methods for detecting and mitigating interactions between elements have been proposed, which ensure time savings during detection and mitigate the consequences of interactions and overall timing parameters with minimal deterioration of their characteristic parameters, and with minimal increase in area and power consumption.

A method based on machine learning algorithms has been developed for predicting interactions between elements in integrated circuits. This method ensures approximately 36,6% time savings on signal integrity analysis with minimal data collection and circuit analysis, at the cost of around 10% loss in the predicted data.

A method for modifying the corresponding wires, considering the architecture of the synchronization signal tree and the design features of the circuit, has been proposed. This method, through optimized combinations of shielding and blocking and relocating the wires of the synchronization signal tree, provides approximately 17,9% mitigation of interaction effects, 16,9% and 19,1% reduction in the overall setup and hold times of sequential elements, with a loss of about 5,66% in power consumption and 3.1% in area.

A method for evaluating and modifying data-carrying wires has been created, taking into account the peculiarities of circuit design, which, through optimized combinations of shielding and repeaters, ensures a reduction in the impact of interactions by approximately 17%, a reduction in the total setup and hold times by 16,3% and 17,6% respectively, at the cost of about 3% more power consumption and 2,9% more area.

The "Crosstalk Detection and Compensation Tool" (CDACT) software tool has been developed to predict interactions between elements and propose mitigation solutions. When applied to modify the wires of the clock tree, it results in a reduction of interactions by 15,3%, a decrease in the total setup and hold times of sequential elements by 14,1% and 15,9% respectively, with a 2,91% increase in area and a 4,58% increase in power consumption. For data wire modifications, the interactions are reduced by 15%, the total setup and hold times are decreased by 13,6% and 14,6% respectively, with a 2,7% increase in area and a 2,7% increase in power consumption.